고정 헤더 영역

상세 컨텐츠

본문

1) MOSFET 구조

<N-Channel MOSFET (NMOS)>

- Enhancement-Mode NMOS

: Vgs > Vt >0

: Normally Off

- Depletion-Mode NMOS

: Vt < 0

: Normally On

채널이 형성되어 있기 때문에 항상 On인 소자입니다.

<P-Channel MOSFET (PMOS)>

- Enhancement-Mode PMOS

: Vt < 0

- Depletion-Mode PMOS

: Vt > 0

NMOS와 마찬가지로 채널이 형성되어 있기 때문에 항상 On인 소자입니다.

2) MOSFET 동작

1. Vgs < Vt

드레인에 전압을 인가하게 되면 PN Junction에 의해 Reverse Bias가 걸리고,

이에 따라 드레인 쪽의 공핍층 (Depletion Layer)가 증가하게 됩니다.

그러나 게이트 전압이 문턱 전압보다 낮기 때문에 채널은 형성되지 않습니다.

2. Vgs > Vt

문턱 전압보다 큰 게이트 전압이 인가되면 반도체 표면에 반전층(채널)이 형성되게 됩니다.

이를 통로로 하여 전자가 이동을 하며 전류가 흐르게 됩니다.

- Small Vds

- Large Vds

Vov와 Vds 간의 차이가 감소함에 따라 드레인 영역의 전하 밀도가 감소하게 됩니다.

따라서 그림과 같은 현상이 발생하게 됩니다.

- Vds = Vov (Vgs - Vt)

드레인에 인가하는 전압이 Vov와 같아지게 되면 채널의 끝부분이 막히는 현상,

즉 Pinch-off(핀치오프) 현상이 발생하게 됩니다.

드레인 전압이 점점 커질 수록 드레인 영역의 공핍층이 점점 커지면서 채널을 막게 되고,

핀치 오프 현상이 발생하고 난 후에는 전류의 양이 더이상 증가하지 않게 됩니다.

이때, 전류가 Saturation(포화)되었다고 이야기 할 수 있습니다.

- Vds > Vov

드레인에 인가하는 전압이 Vov보다 큰 경우, 채널의 길이는 점점 짧아지게 됩니다.

이때, 소스에서 드레인으로 전자가 이동하는 길이 막혔다고 보실 수도 있지만 그렇지 않습니다.

위에서 이야기한 것처럼 드레인 전압의 증가에 따라 전류가 증가는 하지 않지만 계속해서 흐르게 됩니다.

공핍층에 걸린 강한 전계에 의해서 전자가 드레인으로 이동하기 때문입니다.

3) 전류-전압 특성

※ 아주 중요한 개념입니다.

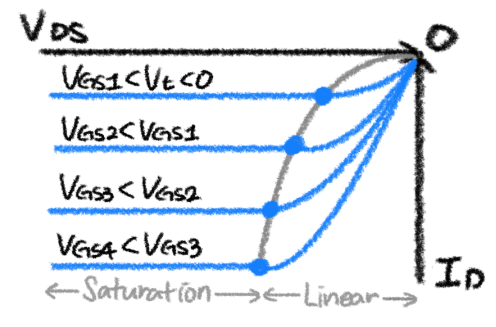

<NMOS>

- Id 대 Vds

게이트 전압이 커질 수록 드레인 전류가 증가하는 것을 확인할 수 있습니다.

- Id 대 Vgs

문턱 전압보다 낮은 게이트 전압에서는 채널이 형성되지 않아 전류가 흐르지 않으며,

문턱 전압보다 큰 게이트 전압에서 채널이 형성됨에 따라 전류가 흐르는 것을 확인할 수 있습니다.

로그 스케일에서 확인을 하면 문턱전압보다 낮은 영역에서도 전류가 미세하게 흐르는 것을 확인할 수 있는데,

이때 흐르는 전류가 Subthreshold Current입니다.

아래에는 추가적으로 PMOS의 전류-전압 특성 그래프를 첨부하도록 하겠습니다.

<PMOS>

- Id 대 Vds

- Id 대 Vgs

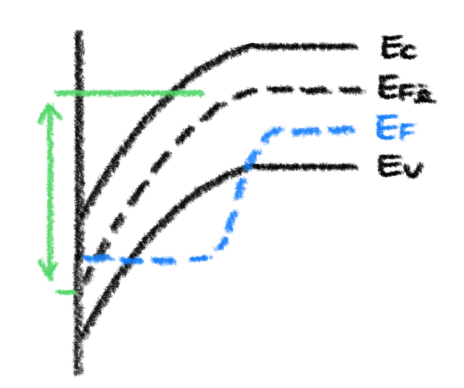

4) Body Effect (Subsstrate Bias Effect)

: 소스와 바디에 역방향 바이어스가 걸리는 경우 문턱전압이 상승하는 효과

모스펫에서 소스와 기판은 항상 0 또는 역방향 바이어스가 되어야 하기 때문에 Vsb는 0 이상이어야 합니다.

다시 말해, 바디에 0 또는 Negative 전압이 인가되어야 합니다.

만약 Vsb가 0보다 작은 경우, 즉 바디에 Positive 전압을 인가하면 소스와 바디의 PN Junction에 순방향 바이어스가 인가되기 때문에 Current Short가 발생합니다.

"0"을 인가한 경우는 앞서 언급한 모스펫 동작과 동일하지만 이후 이어질 내용들에 대한 이해를 높이고자 수식과 함께 설명하도록 하겠습니다.

아래는 0을 인가하였을 때 반전층의 반전 전하를 나타내는 수식입니다.

"Negative 전압"을 인가하면 바디에 위치한 정공들이 바디 쪽으로 이동하면서 Depletion Region (공핍 영역) 확장됩니다.

이 경우에는 반전층, 즉 채널이 산화막 커패시터와 바디 전압에 의해 형성된 공핍층 커패시터에 의해 조절됩니다.

이때 반전층의 반전 전하는 다음과 같습니다.

그리고 여기서 파란색 네모 박스가 바디효과계수입니다.

위에서 언급하였듯이 이 경우에는 소스와 바디, 그리고 드레인과 바디에 역방향 바이어스가 걸리기 때문에 공핍 영역이 크게 확장하여 바디 내부의 전자들이 공핍층 내부의 이온격자 산란에 의해 계면쪽으로 이동하는데 더 큰 힘이 필요하게 됩니다.

이에 따라 문턱전압이 증가하게 됩니다.

문턱전압이 증가하게 되면 결국 전류가 작아지기 때문에 속도가 저하되는 문제가 발생합니다.

따라서 Body Effect가 작을 수록,

문턱전압이 바디 전압에 의해 영향을 적게 받아 최적의 동작을 할 수 있게 됩니다.

※ Body Effect 최소화

Body Effect를 최소화하기 위한 방법은 바디효과계수를 감소시켜야 합니다.

바디효과계수를 줄이기 위해서는 공핍 커패시턴스를 감소시키고, 산화막 커패시턴스를 증가시키는 방법이 있습니다.

특히 산화막 커패시턴스를 증가시키기 위해 게이트 산화막의 두께를 감소시킬 수 있습니다.

그렇지만 게이트 산화막을 계속적으로 줄이게 되면 터널링에 의한 누설전류가 증가하는 이슈가 발생하여

High-K 물질을 사용함으로써 같은 두께로도 더 큰 커패시턴스를 형성함으로써 이를 극복할 수 있습니다.

'반도체공학' 카테고리의 다른 글

| Secondary Effect (2) (0) | 2024.11.04 |

|---|---|

| Secondary Effect (1) (0) | 2024.10.11 |

| MOS Capacitor (MOS 커패시터) (0) | 2024.09.19 |

| MS(Metal-Semiconductor) Junction (MS 접합) (0) | 2024.09.12 |

| PN Junction (PN 접합) (0) | 2024.09.05 |