고정 헤더 영역

상세 컨텐츠

본문

1) DRAM이란?

: Dynamic Random Access Memory

→ Dynamic : 시간이 지나면 데이터가 사라지기 때문에 Refresh가 필요

→ Random Access : 각 비트에 대해 독립적으로 접근(읽기 및 쓰기)하여 데이터의 위치에 상관없이 접근하는 데 동일한 시간 소요

2) DRAM 종류

1. SDR SDRAM (Single Data Rate)

: Rising Edge에 하나의 데이터 전송

2. DDR SDRAM (Double Dara Rate)

: Rising/Falling Edge에 데이터 전송 (한 신호에 두 개의 데이터 전송)

3. LPDDR (Low Power DDR)

: 저전력 DDR

→ Mobile Device에서 사용

4. GDDR (Graphics DDR)

: 데이터버스의 읽기/쓰기 통로 분리

→ Graphic 카드에 사용

5. HBM (High Band Memory)

: 여러 개의 Memory Die가 수직으로 적층

→ AI/Machine Learning을 위한 고대역폭 메모리

6. PIM (Processor In Memory)

: DRAM 메모리에 Processor 기능이 합쳐진 미래형 반도체

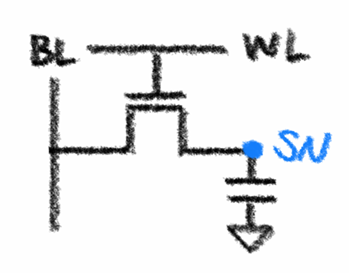

3) DRAM의 구조

DRAM은 1T-1C 구조입니다.

즉, 1개의 Transistor와 1개의 Capacitor로 이루어져 있습니다.

이때, 커패시터에 저장된 데이터를 계속해서 유지되어야 하지만

Transistor가 OFF 상태일 때 누설 전류가 발생하면서 Data가 유실되기 때문에 Refresh 동작이 필요하게 됩니다.

4) DRAM의 동작

1. Read (읽기) Operation

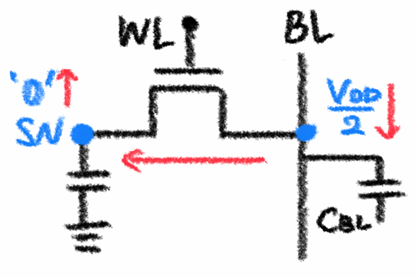

1-1. SN = '1'

① Precharge : BL = Vdd/2

② Sensig (Charge Sharing) : WL = Vpp

Tr.이 On 되면서 전압이 높은 쪽에서 낮은 쪽으로 전류가 발생하게 됩니다.

이에 따라 SN의 전압은 감소하고, BL의 전압은 증가하게 됩니다.

SA (Sense Amplifier)에서 BL 전압의 변화를 감지하여 '1'을 판별하게 됩니다.

③ Refresh (Write Back)

Sensing 과정에서 SN에 저장된 값이 손상되었기 때문에 다시 원래 전압값으로 복구해주어야 합니다.

1-2. SN = '0'

① Precharge : BL = Vdd/2

② Sensig (Charge Sharing) : WL = Vpp

Tr.이 On 되면서 전압이 높은 쪽에서 낮은 쪽으로 전류가 발생하게 됩니다.

이에 따라 SN의 전압은 증가하고, BL의 전압은 감소하게 됩니다.

SA (Sense Amplifier)에서 BL 전압의 변화를 감지하여 '0'을 판별하게 됩니다.

③ Refresh (Write Back)

Sensing 과정에서 SN에 저장된 값이 손상되었기 때문에 다시 원래 전압값으로 복구해주어야 합니다.

2. Program / Write (쓰기) Operation

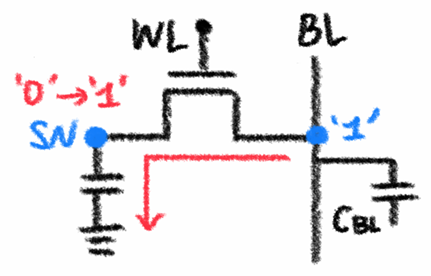

2-1. Write '1'

① BL = '1'

② WL = '1'

Tr.이 On 되면서 전압이 높은 곳에서 낮은 곳으로 전류가 흐르게 됩니다.

이에 따라 커패시터가 충전되어 '1'을 저장하게 됩니다.

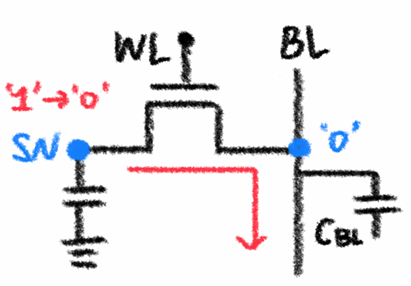

2-2. Write '0'

① BL = '0'

② WL = '1'

Tr.이 On 되면서 전압이 높은 곳에서 낮은 곳으로 전류가 흐르게 됩니다.

이에 따라 커패시터가 방전되어 '0'을 저장하게 됩니다.

'반도체소자' 카테고리의 다른 글

| CMOS (Complementary MOSFET) (0) | 2024.12.16 |

|---|---|

| NAND Flash (0) | 2024.11.19 |