고정 헤더 영역

상세 컨텐츠

본문

이전 포스트에서 DRAM과 NAND Flash에 대해서 알아보았으니 다른 메모리 반도체인 SRAM에 대해 알아보도록 하겠습니다.

1) SRAM이란?

: Static Random Aceess Memory

→ Static : 리프레시 동작 불필요

→ Random Access : 각 비트에 대해 독립적으로 접근(읽기 및 쓰기)하여 데이터의 위치에 상관없이 접근하는 데 동일한 시간 소요

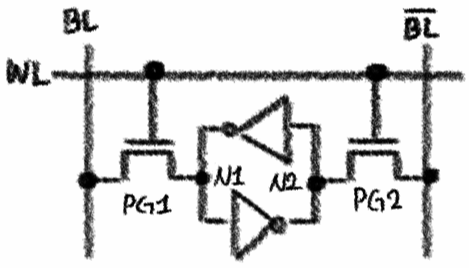

2) SRAM의 구조

SRAM은 두 개의 인버터와 2개의 NMOS, 즉 4개의 NMOS와 2개의 PMOS로 구성되어있습니다.

다시말해, SRAM은 총 6개의 트랜지스터가 1개의 Cell을 구성합니다.

DRAM의 경우 1개의 트랜지스터와 1개의 커패시터로 구성이 되어있다 했었는데,

이에 따라 셀의 크기는 SRMA이 DRAM보다 더 크기 때문에 집적도가 떨어집니다.

3) SRAM의 동작

1. Hold (유지) Operation

WL = '1'을 인가해주면,

CMOS 인버터 두 개가 연결되어 있는 형태로 노드에 저장된 데이터가 계속해서 유지되게 됩니다.

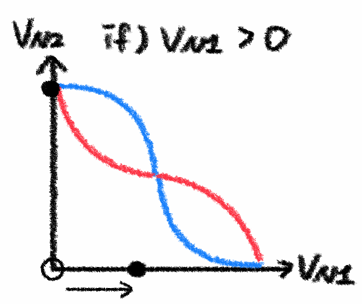

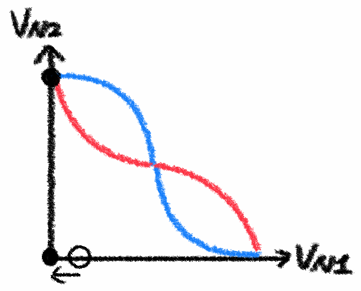

이는 Butterfly Curve를 통해 확인할 수 있습니다.

1.1. Vn1 = '0', Vn2 = '1'

위의 그림에서 보실 수 있듯이 전압에 약간 변화가 생겨도 다시 Stable한 상태로 돌아가는 것을 확인할 수 있습니다.

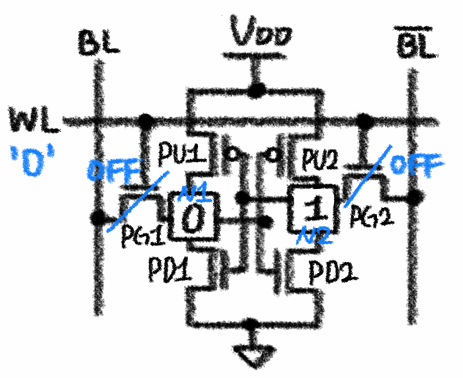

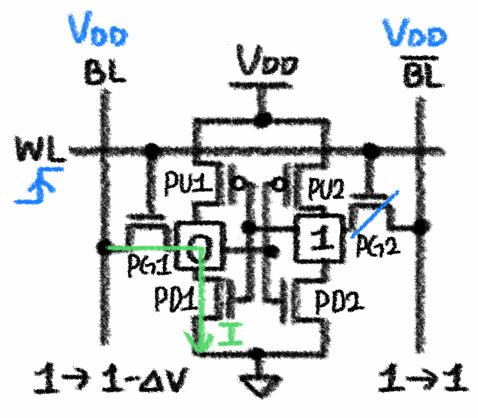

2. Read (읽기) Operation

" Vn1 = '0', Vn2 = '1'"을 가정하고 말씀드리도록 하겠습니다.

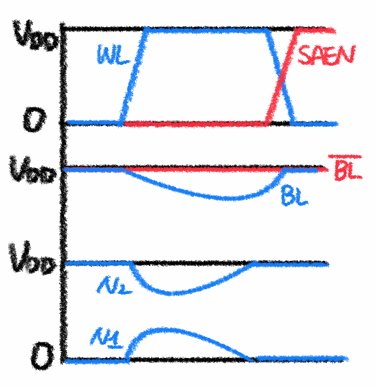

① Precharge : BL = BL' = '1'

② WL = '1'

PG1 Tr.이 On 되고, 반대로 PG2 Tr.은 Off가 됩니다.

PG1에 전류가 발생하여 BL에서 Tr. 로 전류가 흐르게 되고,

이에 따라 BL에 저장되어 있던 전압이 감소하게 되는데 BL의 전위 변화를 통해 '0'을 읽을 수 있습니다.

또한, 전류가 발생하면서 N1 Node의 전위가 상승하게 되는데 이를 유지하기 위한 작업이 필요합니다.

해당 동작이 Recovery입니다.

※ Recovery

앞서 말한 것처럼 전류가 발생하면 N1 Node의 전위가 상승하고 이와 연결된 PU2, PD2에 인가되는 게이트 전압이 증가합니다.

그러면 이에 따라 PD2가 On이 되면서 전류가 발생하고, N2 Node의 전위가 감소하게 됩니다.

완전히 전위가 Flip 되기 전에 유지하기 위해서는 PG1의 컨덕턴스를 감소시키고, PD1의 컨덕턴스를 증가시켜야 합니다.

즉, PG1에는 작은 전류가 흐르도록, PD1에는 많은 전류가 흐르도록 하여 N1 Node의 전위 상승을 방지해주는 것입니다.

Recovery 동작을 통해 다시 원래 상태로 유지되는 것을 확인할 수 있습니다.

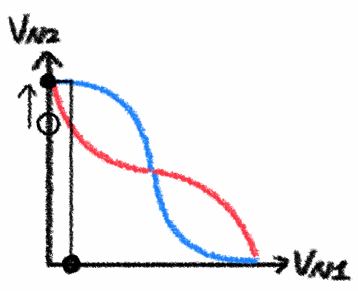

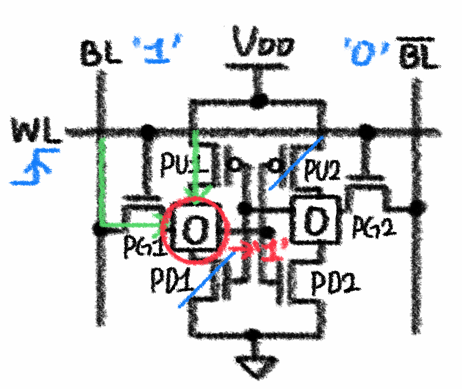

3. Write (쓰기) Operation

" Vn1 = '0' → '1' , Vn2 = '1' → '0'"을 가정하고 말씀드리도록 하겠습니다.

Write 동작을 할 때, 두 Node에 대한 쓰기 동작이 동시에 발생하는 것이 아니라 차례대로 발생합니다.

앞서 Read 동작에서 발생하는 Flip을 막기 위해 PG1의 컨덕턴스를 감소시키고, PD1의 컨덕턴스를 증가시켰습니다.

이로 인해 현재 Node1에 '1' 쓰기 동작을 진행해야 하는데 Flip이 이루어지지 않아 쓰기 동작을 할 수 없게 됩니다.

따라서 Node2에 먼저 '0' 쓰기 동작을 진행해주어야 합니다.

우선 Node1에 '1', Node2에 '0' 쓰기 동작을 하기 위해 BL = '1', BL' = '0'을 인가해줍니다.

① Node2 : '1' → '0'

BL'에 '0'을 인가하면 PG2가 On 되어 Node2에서 BL'로 전류가 발생합니다.

해당 동작에서는 Read와 반대로 무조건 Flip이 가능하도록 설계해야 합니다.

따라서 PU2의 컨덕턴스를 감소시키고, PG2의 컨덕턴스를 증가시켜야 합니다.

즉, PU2에는 작은 전류가 흐르도록, PG2에는 많은 전류가 흐르도록 하여 N2 Node의 전위가 '0'까지 떨어지도록 합니다.

② Node1 : '0' → '1'

N2 Node의 전위가 '0'까지 감소하면 PU1, PD1의 게이트에 0이 인가되고, PU1은 On, PD1은 Off됩니다.

발생하는 전류에 의해 Node1의 전위가 '1'까지 상승하게 되어 '1' 쓰기 동작을 할 수 있게 됩니다.

전체적인 Write 동작은 다음과 같습니다.

이상으로 이번 포스트를 마무리하도록 하겠습니다.

봐주셔서 감사하고, 오류가 있다면 말씀해주시면 감사하겠습니다!

'반도체소자' 카테고리의 다른 글

| CMOS (Complementary MOSFET) (0) | 2024.12.16 |

|---|---|

| NAND Flash (0) | 2024.11.19 |

| DRAM (0) | 2024.11.15 |